JP2005055726A - El display device - Google Patents

El display device Download PDFInfo

- Publication number

- JP2005055726A JP2005055726A JP2003287297A JP2003287297A JP2005055726A JP 2005055726 A JP2005055726 A JP 2005055726A JP 2003287297 A JP2003287297 A JP 2003287297A JP 2003287297 A JP2003287297 A JP 2003287297A JP 2005055726 A JP2005055726 A JP 2005055726A

- Authority

- JP

- Japan

- Prior art keywords

- current

- transistor

- pixel

- signal line

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000011159 matrix material Substances 0.000 claims abstract description 25

- 230000008859 change Effects 0.000 claims description 270

- 238000000034 method Methods 0.000 description 581

- 238000005401 electroluminescence Methods 0.000 description 531

- 235000019557 luminance Nutrition 0.000 description 242

- 238000010586 diagram Methods 0.000 description 163

- 230000002829 reductive effect Effects 0.000 description 137

- 239000010408 film Substances 0.000 description 121

- 239000003990 capacitor Substances 0.000 description 116

- 238000004364 calculation method Methods 0.000 description 98

- 239000000758 substrate Substances 0.000 description 90

- 230000000875 corresponding effect Effects 0.000 description 86

- 230000001276 controlling effect Effects 0.000 description 85

- 238000012545 processing Methods 0.000 description 80

- 230000008569 process Effects 0.000 description 69

- 230000015572 biosynthetic process Effects 0.000 description 55

- 238000006243 chemical reaction Methods 0.000 description 49

- 230000014509 gene expression Effects 0.000 description 49

- 230000015556 catabolic process Effects 0.000 description 48

- 238000005516 engineering process Methods 0.000 description 47

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 47

- 229920005591 polysilicon Polymers 0.000 description 47

- 230000003071 parasitic effect Effects 0.000 description 46

- 230000006870 function Effects 0.000 description 43

- 239000010409 thin film Substances 0.000 description 43

- 238000009826 distribution Methods 0.000 description 36

- 238000012546 transfer Methods 0.000 description 35

- 239000003086 colorant Substances 0.000 description 34

- 230000007423 decrease Effects 0.000 description 34

- 230000000694 effects Effects 0.000 description 33

- 239000010410 layer Substances 0.000 description 27

- 238000007789 sealing Methods 0.000 description 27

- 239000000463 material Substances 0.000 description 26

- 238000007726 management method Methods 0.000 description 23

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 21

- 229910052710 silicon Inorganic materials 0.000 description 21

- 239000010703 silicon Substances 0.000 description 21

- 239000004973 liquid crystal related substance Substances 0.000 description 20

- 239000004065 semiconductor Substances 0.000 description 20

- 229910052751 metal Inorganic materials 0.000 description 19

- 239000002184 metal Substances 0.000 description 19

- 230000003247 decreasing effect Effects 0.000 description 15

- 230000001681 protective effect Effects 0.000 description 15

- 238000003860 storage Methods 0.000 description 15

- 229910021417 amorphous silicon Inorganic materials 0.000 description 14

- 239000012071 phase Substances 0.000 description 14

- 238000013461 design Methods 0.000 description 12

- 230000009467 reduction Effects 0.000 description 12

- 238000001514 detection method Methods 0.000 description 11

- 238000004519 manufacturing process Methods 0.000 description 11

- 238000003672 processing method Methods 0.000 description 11

- 239000011347 resin Substances 0.000 description 11

- 229920005989 resin Polymers 0.000 description 11

- 230000005540 biological transmission Effects 0.000 description 10

- 239000011521 glass Substances 0.000 description 10

- 230000031700 light absorption Effects 0.000 description 10

- 229910052782 aluminium Inorganic materials 0.000 description 9

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 9

- 238000012937 correction Methods 0.000 description 9

- 239000006185 dispersion Substances 0.000 description 9

- 230000000717 retained effect Effects 0.000 description 9

- 230000002195 synergetic effect Effects 0.000 description 9

- 230000008901 benefit Effects 0.000 description 8

- 238000007667 floating Methods 0.000 description 8

- 238000003780 insertion Methods 0.000 description 8

- 230000037431 insertion Effects 0.000 description 8

- 230000035515 penetration Effects 0.000 description 8

- 238000002474 experimental method Methods 0.000 description 7

- 230000033001 locomotion Effects 0.000 description 7

- 239000007769 metal material Substances 0.000 description 7

- 230000002093 peripheral effect Effects 0.000 description 7

- 230000000630 rising effect Effects 0.000 description 7

- 238000004804 winding Methods 0.000 description 7

- HEZMWWAKWCSUCB-PHDIDXHHSA-N (3R,4R)-3,4-dihydroxycyclohexa-1,5-diene-1-carboxylic acid Chemical compound O[C@@H]1C=CC(C(O)=O)=C[C@H]1O HEZMWWAKWCSUCB-PHDIDXHHSA-N 0.000 description 6

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 6

- 238000000137 annealing Methods 0.000 description 6

- 229910052799 carbon Inorganic materials 0.000 description 6

- 230000007547 defect Effects 0.000 description 6

- 238000009792 diffusion process Methods 0.000 description 6

- 238000000605 extraction Methods 0.000 description 6

- 238000005224 laser annealing Methods 0.000 description 6

- 230000007257 malfunction Effects 0.000 description 6

- 238000012986 modification Methods 0.000 description 6

- 230000004048 modification Effects 0.000 description 6

- 239000000049 pigment Substances 0.000 description 6

- 230000004044 response Effects 0.000 description 6

- 230000001052 transient effect Effects 0.000 description 6

- 230000003044 adaptive effect Effects 0.000 description 5

- 230000020169 heat generation Effects 0.000 description 5

- 230000001678 irradiating effect Effects 0.000 description 5

- 238000010030 laminating Methods 0.000 description 5

- 238000005070 sampling Methods 0.000 description 5

- 230000001360 synchronised effect Effects 0.000 description 5

- 238000002834 transmittance Methods 0.000 description 5

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 4

- 241001475178 Dira Species 0.000 description 4

- PEDCQBHIVMGVHV-UHFFFAOYSA-N Glycerine Chemical compound OCC(O)CO PEDCQBHIVMGVHV-UHFFFAOYSA-N 0.000 description 4

- 101100309620 Schizosaccharomyces pombe (strain 972 / ATCC 24843) sck2 gene Proteins 0.000 description 4

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 4

- 238000013459 approach Methods 0.000 description 4

- 229910052804 chromium Inorganic materials 0.000 description 4

- 239000011651 chromium Substances 0.000 description 4

- 230000002596 correlated effect Effects 0.000 description 4

- 238000005520 cutting process Methods 0.000 description 4

- 230000006866 deterioration Effects 0.000 description 4

- 238000011156 evaluation Methods 0.000 description 4

- 239000010931 gold Substances 0.000 description 4

- 230000003287 optical effect Effects 0.000 description 4

- 230000002441 reversible effect Effects 0.000 description 4

- 238000000926 separation method Methods 0.000 description 4

- 229910052709 silver Inorganic materials 0.000 description 4

- 239000004332 silver Substances 0.000 description 4

- LXMSZDCAJNLERA-ZHYRCANASA-N spironolactone Chemical compound C([C@@H]1[C@]2(C)CC[C@@H]3[C@@]4(C)CCC(=O)C=C4C[C@H]([C@@H]13)SC(=O)C)C[C@@]21CCC(=O)O1 LXMSZDCAJNLERA-ZHYRCANASA-N 0.000 description 4

- 208000026082 sterile multifocal osteomyelitis with periostitis and pustulosis Diseases 0.000 description 4

- 230000000007 visual effect Effects 0.000 description 4

- LYCAIKOWRPUZTN-UHFFFAOYSA-N Ethylene glycol Chemical compound OCCO LYCAIKOWRPUZTN-UHFFFAOYSA-N 0.000 description 3

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 3

- 101100420795 Schizosaccharomyces pombe (strain 972 / ATCC 24843) sck1 gene Proteins 0.000 description 3

- 230000002159 abnormal effect Effects 0.000 description 3

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 3

- 239000000853 adhesive Substances 0.000 description 3

- 230000001070 adhesive effect Effects 0.000 description 3

- 239000012790 adhesive layer Substances 0.000 description 3

- 230000002411 adverse Effects 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- 239000013078 crystal Substances 0.000 description 3

- 239000002274 desiccant Substances 0.000 description 3

- 238000007599 discharging Methods 0.000 description 3

- 239000000975 dye Substances 0.000 description 3

- 230000005684 electric field Effects 0.000 description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 230000006872 improvement Effects 0.000 description 3

- 230000001788 irregular Effects 0.000 description 3

- 239000003550 marker Substances 0.000 description 3

- 238000002156 mixing Methods 0.000 description 3

- 239000011368 organic material Substances 0.000 description 3

- 238000003825 pressing Methods 0.000 description 3

- 230000035945 sensitivity Effects 0.000 description 3

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 3

- 238000009966 trimming Methods 0.000 description 3

- 239000004925 Acrylic resin Substances 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- 239000004593 Epoxy Substances 0.000 description 2

- 229910052770 Uranium Inorganic materials 0.000 description 2

- 206010047571 Visual impairment Diseases 0.000 description 2

- 239000011358 absorbing material Substances 0.000 description 2

- 239000011230 binding agent Substances 0.000 description 2

- JOPOVCBBYLSVDA-UHFFFAOYSA-N chromium(6+) Chemical compound [Cr+6] JOPOVCBBYLSVDA-UHFFFAOYSA-N 0.000 description 2

- 239000011248 coating agent Substances 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 238000012217 deletion Methods 0.000 description 2

- 230000037430 deletion Effects 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- 230000005611 electricity Effects 0.000 description 2

- 239000007772 electrode material Substances 0.000 description 2

- 238000005538 encapsulation Methods 0.000 description 2

- 239000003822 epoxy resin Substances 0.000 description 2

- 210000000744 eyelid Anatomy 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 238000009499 grossing Methods 0.000 description 2

- 230000012447 hatching Effects 0.000 description 2

- 210000003128 head Anatomy 0.000 description 2

- 230000017525 heat dissipation Effects 0.000 description 2

- 239000002346 layers by function Substances 0.000 description 2

- 229910052744 lithium Inorganic materials 0.000 description 2

- 238000011068 loading method Methods 0.000 description 2

- 239000011777 magnesium Substances 0.000 description 2

- 230000014759 maintenance of location Effects 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 238000003909 pattern recognition Methods 0.000 description 2

- 229920000647 polyepoxide Polymers 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 239000007787 solid Substances 0.000 description 2

- 239000007790 solid phase Substances 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 230000001629 suppression Effects 0.000 description 2

- 230000002123 temporal effect Effects 0.000 description 2

- 229910052727 yttrium Inorganic materials 0.000 description 2

- RICKKZXCGCSLIU-UHFFFAOYSA-N 2-[2-[carboxymethyl-[[3-hydroxy-5-(hydroxymethyl)-2-methylpyridin-4-yl]methyl]amino]ethyl-[[3-hydroxy-5-(hydroxymethyl)-2-methylpyridin-4-yl]methyl]amino]acetic acid Chemical compound CC1=NC=C(CO)C(CN(CCN(CC(O)=O)CC=2C(=C(C)N=CC=2CO)O)CC(O)=O)=C1O RICKKZXCGCSLIU-UHFFFAOYSA-N 0.000 description 1

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- 229910001148 Al-Li alloy Inorganic materials 0.000 description 1

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- 238000012935 Averaging Methods 0.000 description 1

- 208000013586 Complex regional pain syndrome type 1 Diseases 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 102100040844 Dual specificity protein kinase CLK2 Human genes 0.000 description 1

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 1

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- 108010010803 Gelatin Proteins 0.000 description 1

- 241000587161 Gomphocarpus Species 0.000 description 1

- 101000749291 Homo sapiens Dual specificity protein kinase CLK2 Proteins 0.000 description 1

- 241001237160 Kallima inachus Species 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- 206010027146 Melanoderma Diseases 0.000 description 1

- 229910000861 Mg alloy Inorganic materials 0.000 description 1

- 229910001182 Mo alloy Inorganic materials 0.000 description 1

- 241000255969 Pieris brassicae Species 0.000 description 1

- 239000004743 Polypropylene Substances 0.000 description 1

- 229910019336 PrMnO3 Inorganic materials 0.000 description 1

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 239000000980 acid dye Substances 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 239000001000 anthraquinone dye Substances 0.000 description 1

- 238000000149 argon plasma sintering Methods 0.000 description 1

- 239000000987 azo dye Substances 0.000 description 1

- 239000011324 bead Substances 0.000 description 1

- 230000002457 bidirectional effect Effects 0.000 description 1

- 230000004397 blinking Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 239000005018 casein Substances 0.000 description 1

- BECPQYXYKAMYBN-UHFFFAOYSA-N casein, tech. Chemical compound NCCCCC(C(O)=O)N=C(O)C(CC(O)=O)N=C(O)C(CCC(O)=N)N=C(O)C(CC(C)C)N=C(O)C(CCC(O)=O)N=C(O)C(CC(O)=O)N=C(O)C(CCC(O)=O)N=C(O)C(C(C)O)N=C(O)C(CCC(O)=N)N=C(O)C(CCC(O)=N)N=C(O)C(CCC(O)=N)N=C(O)C(CCC(O)=O)N=C(O)C(CCC(O)=O)N=C(O)C(COP(O)(O)=O)N=C(O)C(CCC(O)=N)N=C(O)C(N)CC1=CC=CC=C1 BECPQYXYKAMYBN-UHFFFAOYSA-N 0.000 description 1

- 235000021240 caseins Nutrition 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000006378 damage Effects 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 238000009795 derivation Methods 0.000 description 1

- 239000003599 detergent Substances 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 239000010432 diamond Substances 0.000 description 1

- 229910003460 diamond Inorganic materials 0.000 description 1

- 238000005553 drilling Methods 0.000 description 1

- 238000004043 dyeing Methods 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- FWQHNLCNFPYBCA-UHFFFAOYSA-N fluoran Chemical compound C12=CC=CC=C2OC2=CC=CC=C2C11OC(=O)C2=CC=CC=C21 FWQHNLCNFPYBCA-UHFFFAOYSA-N 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 230000004927 fusion Effects 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 229920000159 gelatin Polymers 0.000 description 1

- 239000008273 gelatin Substances 0.000 description 1

- 235000019322 gelatine Nutrition 0.000 description 1

- 235000011852 gelatine desserts Nutrition 0.000 description 1

- 239000001046 green dye Substances 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 238000003384 imaging method Methods 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 239000000025 natural resin Substances 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 239000011022 opal Substances 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 230000035699 permeability Effects 0.000 description 1

- ISWSIDIOOBJBQZ-UHFFFAOYSA-N phenol group Chemical group C1(=CC=CC=C1)O ISWSIDIOOBJBQZ-UHFFFAOYSA-N 0.000 description 1

- 239000005011 phenolic resin Substances 0.000 description 1

- 230000001443 photoexcitation Effects 0.000 description 1

- IEQIEDJGQAUEQZ-UHFFFAOYSA-N phthalocyanine Chemical compound N1C(N=C2C3=CC=CC=C3C(N=C3C4=CC=CC=C4C(=N4)N3)=N2)=C(C=CC=C2)C2=C1N=C1C2=CC=CC=C2C4=N1 IEQIEDJGQAUEQZ-UHFFFAOYSA-N 0.000 description 1

- 239000001007 phthalocyanine dye Substances 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229920006289 polycarbonate film Polymers 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 229920006267 polyester film Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 238000006116 polymerization reaction Methods 0.000 description 1

- -1 polypropylene Polymers 0.000 description 1

- 229920001155 polypropylene Polymers 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 239000001044 red dye Substances 0.000 description 1

- 230000004043 responsiveness Effects 0.000 description 1

- 239000000565 sealant Substances 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

- 238000005476 soldering Methods 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 239000000057 synthetic resin Substances 0.000 description 1

- 229920003002 synthetic resin Polymers 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 1

- 239000005341 toughened glass Substances 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- AAAQKTZKLRYKHR-UHFFFAOYSA-N triphenylmethane Chemical compound C1=CC=CC=C1C(C=1C=CC=CC=1)C1=CC=CC=C1 AAAQKTZKLRYKHR-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Abstract

Description

本発明は、有機または無機エレクトロルミネッセンス(EL)素子を用いたEL表示パネルなどの自発光表示パネルに関するものである。また、これらの表示パネルなどの駆動回路(IC)に関するものである。EL表示パネルなどの駆動方法と駆動回路およびそれらを用いた情報表示装置などに関するものである。 The present invention relates to a self-luminous display panel such as an EL display panel using an organic or inorganic electroluminescence (EL) element. The present invention also relates to a drive circuit (IC) such as these display panels. The present invention relates to a driving method and a driving circuit for an EL display panel and the like, an information display device using them, and the like.

一般に、アクティブマトリクス型表示装置では、多数の画素をマトリクス状に並べ、与えられた映像信号に応じて画素毎に光強度を制御することによって画像を表示する。たとえば、電気光学物質として液晶を用いた場合は、各画素に書き込まれる電圧に応じて画素の透過率が変化する。電気光学変換物質として有機エレクトロルミネッセンス(EL)材料を用いたアクティブマトリクス型の画像表示装置は画素に書き込まれる電流に応じて発光輝度が変化する。 In general, in an active matrix display device, an image is displayed by arranging a large number of pixels in a matrix and controlling the light intensity for each pixel in accordance with a given video signal. For example, when liquid crystal is used as the electro-optical material, the transmittance of the pixel changes according to the voltage written to each pixel. In an active matrix image display device using an organic electroluminescence (EL) material as an electro-optic conversion substance, light emission luminance changes according to a current written to a pixel.

液晶表示パネルは、各画素はシャッタとして動作し、バックライトからの光を画素であるシャッタでオンオフさせることにより画像を表示する。有機EL表示パネルは各画素に発光素子を有する自発光型である。そのため、有機EL表示パネルは、液晶表示パネルに比べて画像の視認性が高い、バックライトが不要、応答速度が速い等の利点を有する。 In the liquid crystal display panel, each pixel operates as a shutter, and an image is displayed by turning on and off light from a backlight with a shutter that is a pixel. The organic EL display panel is a self-luminous type having a light emitting element in each pixel. Therefore, the organic EL display panel has advantages such as higher image visibility than the liquid crystal display panel, no backlight, and high response speed.

有機EL表示パネルは各発光素子(画素)の輝度は電流量によって制御される。つまり、発光素子が電流駆動型あるいは電流制御型であるという点で液晶表示パネルとは大きく異なる。 In the organic EL display panel, the luminance of each light emitting element (pixel) is controlled by the amount of current. That is, it is greatly different from the liquid crystal display panel in that the light emitting element is a current drive type or a current control type.

有機EL表示パネルも単純マトリクス方式とアクティブマトリクス方式の構成が可能である。前者は構造が単純であるものの大型かつ高精細の表示パネルの実現が困難である。しかし、安価である。後者は大型、高精細表示パネルを実現できる。しかし、制御方法が技術的に難しい、比較的高価であるという課題がある。現在では、アクティブマトリクス方式の開発が盛んに行われている。アクティブマトリクス方式は、各画素に設けた発光素子に流れる電流を画素内部に設けた薄膜トランジスタ(トランジスタ)によって制御する。 The organic EL display panel can also be configured in a simple matrix system and an active matrix system. Although the former has a simple structure, it is difficult to realize a large and high-definition display panel. However, it is cheap. The latter can realize a large, high-definition display panel. However, there is a problem that the control method is technically difficult and relatively expensive. At present, active matrix systems are actively developed. In the active matrix system, a current flowing through a light emitting element provided in each pixel is controlled by a thin film transistor (transistor) provided in the pixel.

このアクティブマトリクス方式の有機EL表示パネルの一画素分の等価回路を図46に示す(たとえば、特許文献1参照)。画素16は発光素子であるEL素子15、第1のトランジスタ11a、第2のトランジスタ11bおよび蓄積容量19からなる。発光素子15は有機エレクトロルミネッセンス(EL)素子である。本発明では、EL素子15に電流を供給(制御)するトランジスタ11aを駆動用トランジスタ11と呼ぶ。また、図46のトランジスタ11bのように、スイッチとして動作するトランジスタをスイッチ用トランジスタ11と呼ぶ。

An equivalent circuit for one pixel of this active matrix organic EL display panel is shown in FIG. 46 (see, for example, Patent Document 1). The

有機EL素子15は多くの場合、整流性があるため、OLED(有機発光ダイオード)と呼ばれることがある。図46などでは発光素子15としてダイオードの記号を用いている。

Since the

ただし、本発明における発光素子15はOLEDに限るものではなく、素子15に流れる電流量によって輝度が制御されるものであればよい。たとえば、無機EL素子が例示される。その他、半導体で構成される白色発光ダイオードが例示される。また、一般的な発光ダイオードが例示される。その他、発光トランジスタでもよい。また、発光素子15は必ずしも整流性が要求されるものではない。双方向性ダイオードであってもよい。本発明のEL素子15はこのいずれでもよい。

However, the

図46の例では、Pチャンネル型のトランジスタ11aのソース端子(S)をVdd(電源電位)とし、EL素子15のカソード(陰極)は接地電位(Vss)に接続される。一方、アノード(陽極)はトランジスタ11bのドレイン端子(D)に接続されている。一方、Pチャンネル型のトランジスタ11aのゲート端子はゲート信号線17aに接続され、ソース端子はソース信号線18に接続され、ドレイン端子は蓄積容量19およびトランジスタ11aのゲート端子(G)に接続されている。

In the example of FIG. 46, the source terminal (S) of the P-

画素16を動作させるために、まず、ゲート信号線17aを選択状態とし、ソース信号線18に輝度情報を表す映像信号を印加する。すると、トランジスタ11aが導通し、蓄積容量19が充電又は放電され、トランジスタ11bのゲート電位は映像信号の電位に一致する。ゲート信号線17aを非選択状態とすると、トランジスタ11aがオフになり、トランジスタ11bは電気的にソース信号線18から切り離される。しかし、トランジスタ11aのゲート電位は蓄積容量(コンデンサ)19によって安定に保持される。トランジスタ11aを介して発光素子15に流れる電流は、トランジスタ11aのゲート/ソース端子間電圧Vgsに応じた値となり、発光素子15はトランジスタ11aを通って供給される電流量に応じた輝度で発光し続ける。

液晶表示パネルは、自発光デバイスではないため、バックライトを用いないと画像を表示できないという問題点がある。バックライトを構成するためには所定の厚みが必要であるため、表示パネルの厚みが厚くなるという問題があった。また、液晶表示パネルでカラー表示を行うためには、カラーフィルターを使用する必要がある。そのため、光利用効率が低いという問題点があった。また、色再現範囲が狭いという問題点があった。 Since the liquid crystal display panel is not a self-luminous device, there is a problem that an image cannot be displayed unless a backlight is used. Since a predetermined thickness is required to configure the backlight, there is a problem that the thickness of the display panel is increased. In order to perform color display on the liquid crystal display panel, it is necessary to use a color filter. Therefore, there is a problem that the light utilization efficiency is low. There is also a problem that the color reproduction range is narrow.

有機EL表示パネルは、低温ポリシリコントランジスタアレイを用いてパネルを構成する。しかし、有機EL素子は、電流により発光するため、トランジスタの特性にバラツキがあると、表示ムラが発生するという課題があった。 The organic EL display panel is configured by using a low-temperature polysilicon transistor array. However, since the organic EL element emits light by current, there is a problem that display unevenness occurs when the transistor characteristics vary.

表示ムラは、画素を電流プログラム方式の構成を採用することにより低減することが可能である。電流プログラムを実施するためには、電流駆動方式のドライバ回路が必要である。しかし、電流駆動方式のドライバ回路にも電流出力段を構成するトランジスタ素子にバラツキが発生する。そのため、各出力端子からの階調出力電流にバラツキが発生し、良好な画像表示ができないという課題があった。 Display unevenness can be reduced by adopting a current programming system for the pixels. In order to implement the current program, a current drive type driver circuit is required. However, variation also occurs in the transistor elements constituting the current output stage in the current drive type driver circuit. For this reason, there is a problem in that the gradation output current from each output terminal varies and a good image display cannot be performed.

この目的を達成するために本発明のEL表示パネル(EL表示装置)のドライバ回路は、単位電流を出力する複数のトランジスタを具備し、このトランジスタの個数を変化させることにより出力電流を出力するものである。また、多段のカレントミラー回路で構成されたことを特徴としている。信号の受け渡しが電圧受け渡しとなるトランジスタ群は密に形成し、カレントミラー回路の群との信号の受け渡しは、電流受け渡しの構成を採用する。また、基準電流は、複数のトランジスタで行う。 In order to achieve this object, the driver circuit of the EL display panel (EL display device) of the present invention includes a plurality of transistors that output unit current, and outputs output current by changing the number of transistors. It is. Further, it is characterized by being composed of a multi-stage current mirror circuit. A transistor group in which signal transfer is voltage transfer is formed densely, and signal transfer with the current mirror circuit group adopts a current transfer configuration. The reference current is performed by a plurality of transistors.

本発明のソースドライバ回路は、カントミラー回路を構成するトランジスタが隣接するように形成しているので、しきい値のずれによる出力電流のばらつきが小さく。したがって、EL表示パネルの輝度むらの発生を抑制することが可能となり、その実用的効果は大きい。 Since the source driver circuit of the present invention is formed so that the transistors constituting the cant mirror circuit are adjacent to each other, variation in output current due to a shift in threshold value is small. Therefore, it is possible to suppress the occurrence of luminance unevenness in the EL display panel, and its practical effect is great.

また、本発明の表示パネル、表示装置等は、高画質、良好な動画表示性能、低消費電力、低コスト化、高輝度化等のそれぞれの構成に応じて特徴ある効果を発揮する。 In addition, the display panel, the display device, and the like of the present invention exhibit distinctive effects according to their respective configurations such as high image quality, good moving image display performance, low power consumption, low cost, and high luminance.

なお、本発明を用いれば、低消費電力の情報表示装置などを構成できるので、電力を消費しない。また、小型軽量化できるので、資源を消費しない。また、高精細の表示パネルであっても十分に対応できる。したがって、地球環境、宇宙環境に優しいこととなる。 Note that if the present invention is used, a low power consumption information display device or the like can be configured, so that power is not consumed. Moreover, since it can be reduced in size and weight, resources are not consumed. Further, even a high-definition display panel can be sufficiently handled. Therefore, it is friendly to the global environment and space environment.

本明細書において各図面は理解を容易にまたは/および作図を容易にするため、省略または/および拡大縮小した箇所がある。たとえば、図11に図示する表示パネルの断面図では薄膜封止膜111などを十分厚く図示している。一方、図10において、封止フタ85は薄く図示している。また、省略した箇所もある。たとえば、本発明の表示パネルなどでは、反射防止のために円偏光板などの位相フィルムが必要である。しかし、本明細書の各図面では省略している。以上のことは以下の図面に対しても同様である。また、同一番号または、記号等を付した箇所は同一もしくは類似の形態もしくは材料あるいは機能もしくは動作を有する。

In the present specification, each drawing is omitted or / and enlarged or reduced for easy understanding and / or drawing. For example, in the cross-sectional view of the display panel shown in FIG. 11, the thin

なお、各図面等で説明した内容は特に断りがなくとも、他の実施例等と組み合わせることができる。たとえば、図8の表示パネルにタッチパネルなどを付加し、図157、図159から図161に図示する情報表示装置とすることができる。また、拡大レンズ1582を取り付け、ビデオカメラ(図159など参照のこと)などに用いるビューファインダ(図58を参照のこと)を構成することもできる。

Note that the contents described in the drawings and the like can be combined with other embodiments and the like without particular notice. For example, a touch panel or the like is added to the display panel of FIG. 8, and the information display device illustrated in FIGS. 157 and 159 to 161 can be obtained. Further, a viewfinder (see FIG. 58) used for a video camera (see FIG. 159, etc.) can be configured by attaching a

また、図4、図15、図18、図21、図23、図29、図30、図35、図36、図40、図41、図44、図100〜図110、図125〜図131、図133〜図146、図197〜図205、図234〜図244、図255〜図264、図276〜図302、図327〜図336、図355〜図358、図362〜図373、図381~図384、図386、図396〜図398、図404〜図406などで説明した本発明の駆動方法は、いずれの本発明の表示装置または表示パネルに適用することができる。 4, 15, 18, 21, 23, 29, 30, 35, 36, 40, 41, 44, 100 to 110, 125 to 131, 133 to 146, 197 to 205, 234 to 244, 255 to 264, 276 to 302, 327 to 336, 355 to 358, 362 to 373, and 381 The driving method of the present invention described in FIGS. 384, 386, 396 to 398, and 404 to 406 can be applied to any display device or display panel of the present invention.

なお、本明細書では、駆動用トランジスタ11、スイッチング用トランジスタ11は薄膜トランジスタとして説明するが、これに限定するものではない。薄膜ダイオード(TFD)、リングダイオードなどでも構成することができる。また、薄膜素子に限定するものではなく、シリコンウエハに形成したトランジスタでもものでもよい。基板71をシリコンウエハで形成すればよい。もちろん、FET、MOS−FET、MOSトランジスタ、バイポーラトランジスタでもよい。これらも基本的に薄膜トランジスタである。その他、バリスタ、サイリスタ、リングダイオード、ホトダオード、ホトトランジスタ、PLZT素子などでもよいことは言うまでもない。つまり、本発明のトランジスタ素子11、ゲートドライバ回路12、ソースドライバ回路14などは、これらのいずれでも使用することができる。

Note that in this specification, the driving

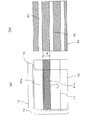

以下、本発明のELパネルについて図面を参照しながら説明をする。有機EL表示パネルは、図10に示すように、画素電極としての透明電極105が形成されたガラス板71(アレイ基板)上に、電子輸送層、発光層、正孔輸送層などからなる少なくとも1層の有機機能層(EL層)15、及び金属電極(反射膜)(カソード)106が積層されたものである。透明電極(画素電極)105である陽極(アノード)にプラス、金属電極(反射電極)106の陰極(カソード)にマイナスの電圧を加え、すなわち、透明電極105及び金属電極106間に直流を印加することにより、有機機能層(EL層)15が発光する。

Hereinafter, the EL panel of the present invention will be described with reference to the drawings. As shown in FIG. 10, the organic EL display panel includes at least one of an electron transport layer, a light emitting layer, a hole transport layer, and the like on a glass plate 71 (array substrate) on which a

金属電極106には、リチウム、銀、アルミニウム、マグネシウム、インジウム、銅または各々の合金等の仕事関数が小さなものを用いることが好ましい。特に、例えばAl−Li合金を用いることが好ましい。また、透明電極105には、ITO等の仕事関数の大きな導電性材料または金等を用いることができる。なお、金を電極材料として用いた場合、電極は半透明の状態となる。なお、ITOはIZOなどの他の材料でもよい。この事項は他の画素電極105に対しても同様である。

The

なお、封止フタ85とアレイ基板71との空間には乾燥剤107を配置する。これは、有機EL膜15は湿度に弱いためである。乾燥剤107によりシール剤を浸透する水分を吸収し有機EL膜15の劣化を防止する。

A

EL表示パネル(EL表示装置)の課題として、パネル内部で発生するハレーションを原因とするコントラスト低下がある。EL素子15(画素16)から発生した光がパネル内部に閉じ込められ乱反射するために発生する。 A problem of an EL display panel (EL display device) is a reduction in contrast caused by halation occurring inside the panel. This occurs because light generated from the EL element 15 (pixel 16) is confined within the panel and diffusely reflected.

この課題を解決するために、本発明では、図388に図示するように、画像表示に非有効な表示領域(無効領域)に光吸収膜3881を形成または配置している。光吸収膜3881を形成することにより、画素16から発生した光(光の軌跡3882で示す)が基板71などで乱反射し、発生するハレーションによる表示コントラスト低下を抑制することができる。

In order to solve this problem, in the present invention, as shown in FIG. 388, a

なお、無効領域とは、基板71あるいはフタ85の側面、基板71かつ表示領域以外(たとえば、ゲートドライバ12が形成された領域など)、フタ85の全面(下取り出しの場合)などである。

Note that the invalid area includes the side surface of the

図388に図示するように、基板71内で乱反射する光3883が光吸収膜3881で吸収される。封止フタ85を黒色材料などで形成することも有効である。

As illustrated in FIG. 388, light 3883 that is irregularly reflected in the

図388(a)はパネル端部を斜め形状に形成あるいは構成している。斜め形状に形成あるいは構成することにより光吸収膜3881の形成面積を広くすることができる。したがって、パネルの基板71内でハレーションする光(光の軌跡3882)を効率より吸収することができ、表示コントラストを向上できる。

In FIG. 388 (a), the end of the panel is formed or configured in an oblique shape. The formation area of the

光吸収膜を構成する物質としては、アクリル樹脂などの有機材料にカーボンを含有させたもの、黒色の色素あるいは顔料を有機樹脂中に分散させたもの、カラーフィルターの様にゼラチンやカゼインを黒色の酸性染料で染色したものが例示される。その他、単一で黒色となるフルオラン系色素を発色させて用いたものでもよく、緑色系色素と赤色系色素とを混合した配色ブラックを用いることもできる。また、スパッタにより形成されたPrMnO3膜、プラズマ重合により形成されたフタロシアニン膜等が例示される。 Substances that make up the light absorption film include organic materials such as acrylic resins containing carbon, black pigments or pigments dispersed in organic resins, and gelatin or casein as a color filter. What was dye | stained with the acid dye is illustrated. In addition, a single black fluoran dye may be used, and a color scheme black obtained by mixing a green dye and a red dye may also be used. Examples thereof include a PrMnO3 film formed by sputtering and a phthalocyanine film formed by plasma polymerization.

以上の材料はすべて黒色の材料であるが、光吸収膜としては、表示素子が発生する光色に対し、補色の関係の材料を用いても良い。例えば、カラーフィルター用の光吸収材料を望ましい光吸収特性が得られるように改良して用いれば良い。基本的には前記した黒色吸収材料と同様に、色素を用いて天然樹脂を染色したものを用いても良い。また、色素を合成樹脂中に分散した材料を用いることができる。色素の選択の範囲は黒色色素よりもむしろ幅広く、アゾ染料、アントラキノン染料、フタロシアニン染料、トリフェニルメタン染料などから適切な1種、もしくはそれらのうち2種類以上の組み合わせでも良い。 The above materials are all black materials, but as the light absorption film, a material having a complementary color with respect to the light color generated by the display element may be used. For example, a light-absorbing material for a color filter may be used so as to obtain desired light absorption characteristics. Basically, a material obtained by dyeing a natural resin with a pigment may be used in the same manner as the black absorbing material described above. Further, a material in which a pigment is dispersed in a synthetic resin can be used. The selection range of the pigment is wider than the black pigment, and may be one suitable from azo dye, anthraquinone dye, phthalocyanine dye, triphenylmethane dye, or a combination of two or more thereof.

また、光吸収膜としては金属材料を用いてもよい。たとえば、六価クロムが例示される。六価クロムは黒色であり、光吸収膜として機能する。その他、オパールガラス、酸化チタンなどの光散乱材料であってもよい。光を散乱させることにより、結果的に光を吸収することと等価になるからである。 Further, a metal material may be used as the light absorption film. For example, hexavalent chromium is exemplified. Hexavalent chromium is black and functions as a light absorbing film. In addition, light scattering materials such as opal glass and titanium oxide may be used. This is because scattering the light is equivalent to absorbing the light as a result.

以上の事項は、図11などの構成にも適用することができることは言うまでもない。 Needless to say, the above items can also be applied to the configuration of FIG.

図10はガラスのフタ85を用いて封止する構成であるが、図11のようにフィルム(薄膜でもよい。つまり、薄膜封止膜である)111を用いた封止であってもよい。たとえば、封止フィルム(薄膜封止膜)111としては電解コンデンサのフィルムにDLC(ダイヤモンド ライク カーボン)を蒸着したものを用いることが例示される。このフィルムは水分浸透性が極めて悪い(防湿性能が高い)。このフィルムを封止膜111として用いる。また、DLC(ダイヤモンド ライク カーボン)膜などを電極106の表面に直接蒸着する構成ものよいことは言うまでもない。その他、樹脂薄膜と金属薄膜を多層に積層して、薄膜封止膜を構成してもよい。

FIG. 10 shows a configuration in which sealing is performed using a

薄膜の膜厚はn・d(nは薄膜の屈折率、複数の薄膜が積層されている場合はそれらの屈折率を総合(各薄膜のn・dを計算)にして計算する。dは薄膜の膜厚、複数の薄膜が積層されている場合はそれらの屈折率を総合して計算する。)が、EL素子15の発光主波長λ以下となるようにするとよい。この条件を満足させることにより、EL素子15からの光取り出し効率が、ガラス基板で封止した場合に比較して2倍以上になる。また、アルミニウムと銀の合金あるいは混合物あるいは積層物を形成してもよい。

The film thickness of the thin film is calculated by n · d (where n is the refractive index of the thin film, and when a plurality of thin films are stacked, the refractive indexes thereof are combined (calculate n · d of each thin film)). When the plurality of thin films are laminated, their refractive indexes are calculated together.) Is preferably equal to or less than the emission main wavelength λ of the

以上のようにフタ85を用いず、封止膜111で封止する構成を薄膜封止と呼ぶ。基板71側から光を取り出す「下取り出し(図10を参照、光取り出し方向は図10の矢印方向である)」の場合の薄膜封止は、EL膜を形成後、EL膜上にカソードとなるアルミ電極を形成する。次にこのアルミ膜上に緩衝層としての樹脂層を形成する。緩衝層としては、アクリル、エポキシなどの有機材料が例示される。また、膜厚は1μm以上10μm以下の厚みが適する。さらに好ましくは、膜厚は2μm以上6μm以下の厚みが適する。この緩衝膜上の封止膜74を形成する。緩衝膜がないと、応力によりEL膜の構造が崩れ、筋状に欠陥が発生する。封止膜111は前述したように、DLC(ダイヤモンド ライク カーボン)、あるいは電界コンデンサの層構造(誘電体薄膜とアルミ薄膜とを交互に多層蒸着した構造)が例示される。

A configuration in which sealing is performed with the sealing

EL層15側から光を取り出す「上取り出し図11を参照、光取り出し方向は図11の矢印方向である」の場合の薄膜封止は、EL膜15を形成後、EL膜15上にカソード(アノード)となるAg−Mg膜を20オングストローム以上300オングストロームの膜厚で形成する。その上に、ITOなどの透明電極を形成して低抵抗化する。次にこの電極膜上に緩衝層としての樹脂層を形成する。この緩衝膜上に封止膜111を形成する。

In the case of extracting light from the

有機EL層15から発生した光の半分は、反射膜106で反射され、アレイ基板71と透過して出射される。しかし、反射膜106には外光を反射し写り込みが発生して表示コントラストを低下させる。この対策のために、アレイ基板71にλ/4板108および偏光板(偏光フィルム)109を配置している。これらは一般的に円偏光板(円偏光シート)と呼ばれる。

Half of the light generated from the

なお、画素が反射電極の場合はEL層15から発生した光は上方向に出射される。したがって、位相板108および偏光板109は光出射側に配置することはいうまでもない。なお、反射型画素は、画素電極105を、アルミニウム、クロム、銀などで構成して得られる。また、画素電極105の表面に、凸部(もしくは凹凸部)を設けることで有機EL層15との界面が広くなり発光面積が大きくなり、また、発光効率が向上する。なお、カソード106(アノード105)となる反射膜を透明電極に形成する、あるいは反射率を30%以下に低減できる場合は、円偏光板は不要である。写り込みが大幅に減少するからである。また、光の干渉も低減し望ましい。

When the pixel is a reflective electrode, the light generated from the

トランジスタ11はLDD(lightly doped drain)構造を採用することが好ましい。また、本明細書ではEL素子として有機EL素子(OEL、PEL、PLED、OLEDなど多種多様な略称で記述される)15を例にあげて説明するがこれに限定するものではなく、無機EL素子にも適用されることは言うまでもない。

The

まず、有機EL表示パネルに用いられるアクティブマトリックス方式は、

特定の画素を選択し、必要な表示情報を与えられること。

1フレーム期間を通じてEL素子に電流を流すことができることという2つの条件を満足させなければならない。

First, the active matrix method used for organic EL display panels is:

A specific pixel can be selected and given display information can be given.

Two conditions must be satisfied that current can flow through the EL element throughout one frame period.

この2つの条件を満足させるため、図46に図示する従来の有機ELの画素構成では、第1のトランジスタ11bは画素を選択するためのスイッチング用トランジスタ、第2のトランジスタ11aはEL素子(EL膜)15に電流を供給するための駆動用トランジスタとする。

In order to satisfy these two conditions, in the conventional organic EL pixel configuration shown in FIG. 46, the

この構成を用いて階調を表示させる場合、駆動用トランジスタ11aのゲート電圧として階調に応じた電圧を印加する必要がある。したがって、駆動用トランジスタ11aのオン電流のばらつきがそのまま表示に現れる。

In the case of displaying gradation using this configuration, it is necessary to apply a voltage corresponding to the gradation as the gate voltage of the driving

トランジスタのオン電流は単結晶で形成されたトランジスタであれば、きわめて均一であるが、安価なガラス基板に形成することのできる形成温度が450度以下の低温ポリシリ技術で形成した低温多結晶トタンジスタでは、そのしきい値のばらつきが±0.2V〜0.5Vの範囲でばらつきがある。そのため、駆動用トランジスタ11aを流れるオン電流がこれに対応してばらつき、表示にムラが発生する。これらのムラは、しきい値電圧のばらつきのみならず、トランジスタの移動度、ゲート絶縁膜の厚みなどでも発生する。また、トランジスタ11の劣化によっても特性は変化する。

The on-current of a transistor is very uniform if it is a transistor formed of a single crystal, but in a low-temperature polycrystalline transistor formed by low-temperature polysilicon technology that can be formed on an inexpensive glass substrate with a formation temperature of 450 degrees or less. The threshold value varies in the range of ± 0.2V to 0.5V. For this reason, the on-current flowing through the driving

この現象は、低温ポリシリコン技術に限定されるものではなく、プロセス温度が450度(摂氏)以上の高温ポリシリコン技術でも、固相(CGS)成長させた半導体膜を用いてトランジスタなどを形成したものでも発生する。その他、有機トランジスタでも発生する。アモルファスシリコントランジスタでも発生する。 This phenomenon is not limited to low-temperature polysilicon technology, and transistors and the like are formed using solid-phase (CGS) grown semiconductor films even in high-temperature polysilicon technology with a process temperature of 450 degrees Celsius or higher. Even things can occur. In addition, it occurs in organic transistors. It also occurs in amorphous silicon transistors.

以下に説明する本発明は、これらの技術に対応し、対策できる構成あるいは方式である。なお、本明細書では低温ポリシリコン技術で形成したトランジスタを主として説明する。 The present invention described below is a configuration or method that can cope with these techniques. In this specification, a transistor formed by low-temperature polysilicon technology will be mainly described.

したがって、図46のように、電圧を書き込むことにより、階調を表示させる方法では、均一な表示を得るために、デバイスの特性を厳密に制御する必要がある。しかし、現状の低温多結晶ポリシリコントランジスタなどではこのバラツキを所定範囲以内の抑えるというスペックを満足できない。 Therefore, as shown in FIG. 46, in the method of displaying gradation by writing a voltage, it is necessary to strictly control the device characteristics in order to obtain a uniform display. However, the current low-temperature polycrystalline polysilicon transistor and the like cannot satisfy the specification of suppressing this variation within a predetermined range.

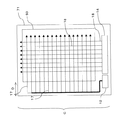

本発明のEL表示装置の画素構造は、具体的には図1に示すように単位画素が最低4つからなる複数のトランジスタ11ならびにEL素子により形成される。画素電極はソース信号線と重なるように構成する。つまり、ソース信号線18上に絶縁膜あるいはアクリル材料からなる平坦化膜を形成して絶縁し、この絶縁膜上に画素電極105を形成する。このようにソース信号線18上の少なくとも1部に画素電極を重ねる構成をハイアパーチャ(HA)構造と呼ぶ。不要な干渉光などが低減し、良好な発光状態が期待できる。

Specifically, the pixel structure of the EL display device of the present invention is formed by a plurality of

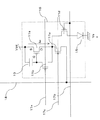

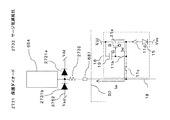

ゲート信号線(第1の走査線)17aをアクティブ(ON電圧を印加)とすることによりEL素子15の駆動用のトランジスタ11aおよびスイッチ用トランジスタ11cを通して、前記EL素子15に流すべき電流値をソースドライバ回路14から流す。また、トランジスタ11aのゲートとドレイン間を短絡するようにトランジスタ11bがゲート信号線17aアクティブ(ON電圧を印加)となることにより開くと共に、トランジスタ11aのゲートとソース間に接続されたコンデンサ(キャパシタ、蓄積容量、付加容量)19にトランジスタ11aのゲート電圧(あるいはドレイン電圧)を記憶する(図3(a)を参照のこと)。

By activating the gate signal line (first scanning line) 17a (applying an ON voltage), the current value to be passed through the

なお、コンデンサ(蓄積容量)19の大きさは、0.2pF以上2pF以下とすることがよく、中でもコンデンサ(蓄積容量)19の大きさは、0.4pF以上1.2pF以下とすることがよい。画素サイズを考慮してコンデンサ19の容量を決定する。1画素に必要な容量をCs(pF)とし、1画素が占める面積(開口率ではない)をSp(平方μm)とすれば、500/S ≦ Cs ≦ 20000/Sとし、さらに好ましくは、1000/Sp ≦ Cs ≦ 10000/Spとなるようにする。なお、トランジスタのゲート容量は小さいので、ここでいうQとは、蓄積容量(コンデンサ)19単独の容量である。

Note that the size of the capacitor (storage capacitor) 19 is preferably 0.2 pF or more and 2 pF or less, and in particular, the size of the capacitor (storage capacitor) 19 is preferably 0.4 pF or more and 1.2 pF or less. . The capacitance of the

ゲート信号線17aを非アクティブ(OFF電圧を印加)、ゲート信号線17bをアクティブとして、電流の流れる経路を前記第1のトランジスタ11a並びにEL素子15に接続されたトランジスタ11dならびに前記EL素子15を含む経路に切り替えて、記憶した電流を前記EL素子15に流すように動作する(図3(b)を参照のこと)。

The

この回路は1画素内に4つのトランジスタ11を有しており、トランジスタ11a のゲートはトランジスタ11bのソースに接続されている。また、トランジスタ11bおよびトランジスタ11cのゲートはゲート信号線17aに接続されている。トランジスタ11bのドレインはトランジスタ11cのソースならびにトランジスタ11dのソースに接続され、トランジスタ11cのドレインはソース信号線18に接続されている。トランジスタ11dのゲートはゲート信号線17bに接続され、トランジスタ11dのドレインはEL素子15のアノード電極に接続されている。

This circuit has four

なお、図1ではすべてのトランジスタはPチャンネルで構成している。Pチャンネルは多少Nチャンネルのトランジスタに比較してモビリティが低いが、耐圧が大きくまた劣化も発生しにくいので好ましい。しかし、本発明はEL素子構成をPチャンネルで構成することのみに限定するものではない。Nチャンネルのみで構成してもよい。また、NチャンネルとPチャンネルの両方を用いて構成してもよい。 In FIG. 1, all the transistors are P-channel. The P channel has a lower mobility than an N channel transistor, but is preferable because it has a high breakdown voltage and is less likely to deteriorate. However, the present invention is not limited to the configuration of the EL element with the P channel. You may comprise only N channel. Moreover, you may comprise using both N channel and P channel.

最適には画素を構成するトランジスタ11をすべてPチャンネルで形成し、内蔵ゲートドライバ12もPチャンネルで形成することが好ましい。このようにアレイをPチャンネルのみのトランジスタで形成することにより、マスク枚数が5枚となり、低コスト化、高歩留まり化を実現できる。

Optimally, it is preferable that all the

以下、さらに本発明の理解を容易にするために、本発明のEL素子構成について図3を用いて説明する。本発明のEL素子構成は2つのタイミングにより制御される。第1のタイミングは必要な電流値を記憶させるタイミングである。このタイミングでトランジスタ11bならびにトランジスタ11cがONすることにより、等価回路として図3(a)となる。ここで、信号線より所定の電流Iwが書き込まれる。これによりトランジスタ11aはゲートとドレインが接続された状態となり、このトランジスタ11aとトランジスタ11cを通じて電流Iwが流れる。したがって、トランジスタ11aのゲート−ソースの電圧はI1が流れるような電圧となる。

Hereinafter, in order to facilitate the understanding of the present invention, the EL element configuration of the present invention will be described with reference to FIG. The EL device configuration of the present invention is controlled by two timings. The first timing is a timing for storing a necessary current value. When the

第2のタイミングはトランジスタ11aとトランジスタ11cが閉じ、トランジスタ11dが開くタイミングであり、そのときの等価回路は図3(b)となる。トランジスタ11aのソース−ゲート間の電圧は保持されたままとなる。この場合、トランジスタ11aは常に飽和領域で動作するため、Iwの電流は一定となる。

The second timing is a timing at which the

このように動作させると、図5に図示するようになる。つまり、図5(a)の51aは表示画面50における、ある時刻での電流プログラムされている画素(行)(書き込み画素行)を示している。この画素(行)51aは、図5(b)に図示するように非点灯(非表示画素(行))とする。他の画素(行)は表示画素(行)53とする(表示領域53の画素16のEL素子15には電流が流れ、EL素子15が発光している)。

When operated in this way, it is as shown in FIG. That is, 51a in FIG. 5A indicates a pixel (row) (write pixel row) in the

図1の画素構成の場合、図3(a)に示すように、電流プログラム時は、プログラム電流Iwがソース信号線18に流れる。この電流Iwがトランジスタ11aを流れ、Iwを流す電流が保持されるように、コンデンサ19に電圧設定(プログラム)される。このとき、トランジスタ11dはオープン状態(オフ状態)である。

In the case of the pixel configuration of FIG. 1, as shown in FIG. 3A, the program current Iw flows through the

次に、EL素子15に電流を流す期間は図3(b)のように、トランジスタ11c、11bがオフし、トランジスタ11dが動作する。つまり、ゲート信号線17aにオフ電圧(Vgh)が印加され、トランジスタ11b、11cがオフする。一方、ゲート信号線17bにオン電圧(Vgl)が印加され、トランジスタ11dがオンする。

Next, during a period in which a current flows through the

このタイミングチャートを図4に図示する。なお、図4などにおいて、括弧内の添え字(たとえば、(1)など)は画素行の番号を示している。つまり、ゲート信号線17a(1)とは、画素行(1)のゲート信号線17aを示している。また、図4の上段の*H(「*」には任意の記号、数値が当てはまり、水平走査線の番号を示す)とは、水平走査期間を示している。つまり、1Hとは第1番目の水平走査期間である。なお、以上の事項は、説明を容易にするためであって、限定(1Hの番号、1H周期、画素行番号の順番など)するものではない。

This timing chart is shown in FIG. In FIG. 4 and the like, subscripts in parentheses (for example, (1) and the like) indicate pixel row numbers. That is, the

図4でわかるように、各選択された画素行(選択期間は、1Hとしている)において、ゲート信号線17aにオン電圧が印加されている時には、ゲート信号線17bにはオフ電圧が印加されている。また、この期間は、EL素子15には電流が流れていない(非点灯状態)。選択されていない画素行において、ゲート信号線17aにオフ電圧が印加され、ゲート信号線17bにはオン電圧が印加されている。また、この期間は、EL素子15に電流が流れている(点灯状態)。

As can be seen from FIG. 4, when a turn-on voltage is applied to the

なお、トランジスタ11aのゲートとトランジスタ11cのゲートは同一のゲート信号線11aに接続している。しかし、トランジスタ11aのゲートとトランジスタ11cのゲートとを異なるゲート信号線11に接続してもよい(図32を参照のこと)。1画素のゲート信号線は3本となる(図1の構成は2本である)。トランジスタ11bのゲートのON/OFFタイミングとトランジスタ11cのゲートのON/OFFタイミングを個別に制御することにより、トランジスタ11aのばらつきによるEL素子15の電流値バラツキをさらに低減することができる。

Note that the gate of the

ゲート信号線17aとゲート信号線17bとを共通にし、トランジスタ11cと11dが異なった導電型(NチャンネルとPチャンネル)とすると、駆動回路の簡略化、ならびに画素の開口率を向上させることが出来る。

When the

このように構成すれば本発明の動作タイミングとしては信号線からの書きこみ経路がオフになる。すなわち所定の電流が記憶される際に、電流の流れる経路に分岐があると正確な電流値がトランジスタ11aのソース(S)−ゲート(G)間容量(コンデンサ)に記憶されない。トランジスタ11cとトランジスタ11dを異なった導電形にすることにより、お互いの閾値を制御することによって走査線の切り替わりのタイミングで必ずトランジスタ11cがオフしたのちに、トランジスタ11dがオンすることが可能になる。

With this configuration, the write path from the signal line is turned off as the operation timing of the present invention. That is, when a predetermined current is stored, if there is a branch in the current flow path, an accurate current value is not stored in the capacitance (capacitor) between the source (S) and the gate (G) of the

ただし、この場合お互いの閾値を正確にコントロールする必要があるのでプロセスの注意が必要である。なお、以上述べた回路は最低4つのトランジスタで実現可能であるが、より正確なタイミングのコントロールあるいは後述するように、ミラー効果低減のためにトランジスタ11eを図2に示すように、カスケード接続してトランジスタの総数が4以上になっても動作原理は同じである。このようにトランジスタ11eを加えた構成とすることにより、トランジスタ11cを介してプログラムした電流がより精度よくEL素子15に流すことができるようになる。

In this case, however, it is necessary to carefully control each other's thresholds, so care must be taken in the process. Although the circuit described above can be realized with at least four transistors, the

なお、本発明の画素構成は図1、図2の構成に限定されるものではない。たとえば、図113のように構成してもよい。図113は、図1の構成に比較してスイッチ素子11dがない。替わりに切り替えスイッチ1131が形成または配置されている。図1のスイッチ11dは駆動用トランジスタ11aからEL素子15に流れる電流をオンオフ(流す、流さない)制御する機能を有する。以降の実施例でも説明をするが、本発明はこのトランジスタ11dのオンオフ制御機能が重要な構成要素である。トランジスタ11dを形成せず、オンオフ機能を実現するのが、図113の構成である。

Note that the pixel configuration of the present invention is not limited to the configurations of FIGS. For example, it may be configured as shown in FIG. 113 does not have the

図113において、切り替えスイッチ1131のa端子は、アノード電圧Vddに接続されている。なお、a端子に印加する電圧はアノード電圧Vddに限定されるものではなく、EL素子15に流れる電流をオフできる電圧であればいずれでもよい。

In FIG. 113, the terminal a of the

切り替えスイッチ1131のb端子は、カソード電圧(図113ではグランドと図示している)に接続されている。なお、b端子に印加する電圧はカソード電圧に限定されるものではなく、EL素子15に流れる電流をオンできる電圧であればいずれでもよい。

The b terminal of the

切り替えスイッチ1131のc端子にはEL素子15のカソード端子が接続されている。なお、切り替えスイッチ1131はEL素子15に流れる電流をオンオフさせる機能を持つものであればいずれでもよい。したがって、図113の形成位置に限定されるものではなく、EL素子15の電流が流れる経路であればいずれでもよい。また、スイッチの機能の限定されるものでもなく、EL素子15に流れる電流をオンオフできればいずれでもよい。つまり、本発明では、EL素子15の電流経路にEL素子15に流す電流をオンオフできるスイッチング手段を具備しればいずれの画素構成でもよい。

The cathode terminal of the

また、オフとは完全に電流が流れない状態を意味するものではない。EL素子15に流れる電流を通常よりも低減できるものであればよい。以上の事項は本発明の他の構成においても同様である。

Further, “off” does not mean a state in which no current flows completely. Any current can be used as long as the current flowing through the

切り替えスイッチ1131は、PチャンネルとNチャンネルのトランジスタを組み合わせることにより容易に実現できるので説明を要さないであろう。たとえば、アナログスイッチを2回路形成すればよい。もちろん、スイッチ1131はEL素子15に流れる電流をオンオフするだけであるから、PチャンネルトランジスタあるいはNチャンネルトランジスタでも形成することができることは言うまでもない。

Since the change-

スイッチ1131がa端子に接続されている時は、EL素子15のカソード端子にVdd電圧が印加される。したがって、駆動用トランジスタ11aのゲート端子Gがいずれの電圧保持状態であってもEL素子15には電流が流れない。したがって、EL素子15は非点灯状態となる。

When the

スイッチ1131がb端子に接続されている時は、EL素子15のカソード端子にGND電圧が印加される。したがって、駆動用トランジスタ11aのゲート端子Gに保持された電圧状態に応じてEL素子15に電流が流れる。したがって、EL素子15は点灯状態となる。

When the

以上のことより図113の画素構成では、駆動用トランジスタ11aとEL素子15間にはスイッチング用トランジスタ11dが形成されていない。しかし、スイッチ1131を制御することによりEL素子15の点灯制御を行うことができる。

From the above, in the pixel configuration of FIG. 113, the switching

図1、図2などの画素構成では、駆動用トランジスタ11aは1画素につき1個である。本発明はこれに限定するものではなく、駆動用トランジスタ11aは1画素に複数個を形成または配置してもよい。図116はその実施例である。図116では1画素に2個の駆動用トランジスタ素子11a1、11a2が形成され、2個の駆動用トランジスタ11a1、11a2のゲート端子は共通のコンデンサ19に接続されている。駆動用トランジスタ11aを複数個形成することにより、プログラムされる電流バラツキが低減するという効果がある。他の構成は、図1などと同様であるので説明を省略する。

In the pixel configuration shown in FIGS. 1 and 2, the number of driving

図1、図2は駆動用トランジスタ11aが出力する電流をEL素子15に流し、前記電流を駆動用トランジスタ11aとEL素子15間に配置されたスイッチング素子11dでオンオフ制御するものであった。しかし、本発明はこれに限定されるものではない。たとえば、図117の構成が例示される。

1 and 2, the current output from the driving

図117の実施例では、EL素子15に流す電流が駆動用トランジスタ11aで制御される。EL素子15に流れる電流をオンオフさせるのはVdd端子とEL素子15間に配置されたスイッチング素子11dで制御される。したがって、本発明はスイッチング素子11dの配置はどこでもよく、EL素子15に流れる電流を制御できるものであればいずれでもよい。動作などは図1などと類似であるので説明を省略する。

In the embodiment of FIG. 117, the current flowing through the

また、図387の画素構成において、すべてのトランジスタはNチャンネルで構成している。しかし、本発明はEL素子構成をNチャンネルで構成することのみに限定するものではない。NチャンネルとPチャンネルの両方を用いて構成してもよい。 Further, in the pixel configuration in FIG. 387, all the transistors are configured by N channels. However, the present invention is not limited to the configuration of the EL element composed of N channels. You may comprise using both N channel and P channel.

以下、図387の画素構成は、2つのタイミングにより制御される。第1のタイミングは必要な電流値を記憶させるタイミングである。 Hereinafter, the pixel configuration in FIG. 387 is controlled by two timings. The first timing is a timing for storing a necessary current value.

このタイミングではゲート信号線17aにオン電圧(Vgh)が印加されることにより、トランジスタ11bならびにトランジスタ11cがONする。また、ゲート信号線17bにオフ電圧(Vgl)が印加され、トランジスタ11dがOFFする。したがって、ソース信号線18より所定の電流Iwが書き込まれる。これによりトランジスタ11aはゲートとドレインが接続された状態となり、このトランジスタ11aとトランジスタ11cを通じてプルグラム電流が流れる。

At this timing, an ON voltage (Vgh) is applied to the

第2のタイミングはゲート信号線17aにオフ電圧が印加され、ゲート信号線17bにオン電圧が印加される。したがって、トランジスタ11aとトランジスタ11cが閉じ、トランジスタ11dが開く。この場合、トランジスタ11aは常に飽和領域で動作するため、Iwの電流は一定となる。

In the second timing, an off voltage is applied to the

トランジスタ11aの特性のバラツキはトランジスタサイズに相関がある。特性バラツキを小さくするため、第1のトランジスタ11aのチャンネル長が5μm以上100μm以下とすることが好ましい。さらに好ましくは、第1のトランジスタ11aのチャンネル長が10μm以上50μm以下とすることが好ましい。これは、チャンネル長Lを長くした場合、チャンネルに含まれる粒界が増えることによって電界が緩和されキンク効果が低く抑えられるためであると考えられる。

The variation in the characteristics of the

以上のように、本発明は、EL素子15に電流が流れこむ経路、またはEL素子15から電流が流れ出す経路(つまり、EL素子15の電流経路である)にEL素子15に流れる電流を制御する回路手段を構成または形成もしくは配置したものである。

As described above, the present invention controls the current flowing through the

電流プログラム方式の1つであるカレントミラー方式であっても、図114に図示すうように、駆動用トランジスタ11bとEL素子15間にスイッチング素子としてのトランジスタ11gを形成または配置することによりEL素子15に流れる電流をオンオフすることができる(制御することができる)。もちろん、トランジスタ11gは図113のスイッチ1131に置き換えても良い。

Even in the current mirror system which is one of current programming systems, as shown in FIG. 114, an EL element is formed by arranging or arranging a transistor 11g as a switching element between the driving

なお、図114のスイッチング用トランジスタ11d、11cは1本のゲート信号線17aに接続されているが、図115に図示するように、トランジスタ11cはゲート信号線17a1で制御し、トランジスタ11dはゲート信号線17a2で制御するように構成してもよい。図115の構成の方が、画素16の制御の汎用性が高くなる。

114 are connected to one

また、図42(a)に図示するように、トランジスタ11b、11cなどはNチャンネルトランジスタで形成してもよい。また、図42(b)に図示するようにトランジスタ11c、11dなどはPチャンネルトランジスタで形成してもよい。

Further, as illustrated in FIG. 42A, the

以上の画素16の構成は、画素16を構成するトランジスタ数が4または5個以上であった。しかし、本発明はこれに限定するものではない。図261に図示するように5個以上のトランジスタで構成してもよい。図261では、駆動用トランジスタ11a1と11a2を用いることにより、低階調領域でも、書込み不足のない電流プログラムを行うことができる。

In the configuration of the

以下、図261に図示した画素構成の駆動方法について説明をする。図261の画素構成は、図265に示すように3つの駆動状態から構成される。第1の状態を図262に示す。また、第2の状態を図263に示す。また、第3の状態を図264に示す。第1の状態と第2の状態が電流プログラムを行っている状態であり、第3の状態がEL素子15に電流を流し、EL素子15が発光している状態である。なお、スイッチ用トランジスタ11d1をオーブンあるいはクローズさせてduty制御を行うことは、本発明の他の実施例と同様であるので説明を省略する。

Hereinafter, a driving method of the pixel configuration illustrated in FIG. 261 will be described. The pixel configuration in FIG. 261 includes three driving states as shown in FIG. The first state is shown in FIG. The second state is shown in FIG. The third state is shown in FIG. The first state and the second state are states in which current programming is performed, and the third state is a state in which a current is passed through the

図261の画素構成はソース信号線18aとソース信号線18bを有している。基本的には、ソース信号線18aに印加するプログラム電流とソース信号線18bに印加するプログラム電流の差が、駆動用トランジスタ11a1に流れるように電流プログラムされ、この電流がEL素子15に流れる。なお、説明を容易にするため、ソース信号線18aにプログラム電流I1=10μA流すとし、ソース信号線18bにプログラム電流I3=10.1μA流し、駆動用トランジスタ11a1にI1とI3の差であるI2=0.1μAを書き込むものとする。

The pixel configuration in FIG. 261 includes a

第1の状態では、図265に示すように、トランジスタ11c2、トランジスタ11b2がクローズ状態にされ、トランジスタd2、トランジスタ11b1、トランジスタ11d1、トランジスタ11c1がオープン状態にされる。 In the first state, as illustrated in FIG. 265, the transistor 11c2 and the transistor 11b2 are closed, and the transistor d2, the transistor 11b1, the transistor 11d1, and the transistor 11c1 are opened.

図262に図示するようにプログラム電流I1はアノード端子から駆動用トランジスタ11a2を介して、ソース信号線18aに流れる。プログラム電流I1はソースドライバIC14により発生させられる。プログラム電流I1はコンデンサ19bにより保持される(駆動用トランジスタ11a2がプログラム電流I1を流せるように駆動用トランジスタ11a2のゲート端子に電圧が保持される)。他のスイッチ用トランジスタ11はオフ状態である。以上の第1の状態により、駆動用トランジスタ11a2は、プログラム電流I1が流れるようにプログラムされる。

As shown in FIG. 262, the program current I1 flows from the anode terminal to the

第2の状態では、図265に示すように、トランジスタ11d2、トランジスタ11b1、トランジスタ11c1がクローズ状態にされ、トランジスタ11c2、トランジスタ11b2、トランジスタ11d1がオープン状態にされる。 In the second state, as illustrated in FIG. 265, the transistor 11d2, the transistor 11b1, and the transistor 11c1 are closed, and the transistor 11c2, the transistor 11b2, and the transistor 11d1 are opened.

図263に図示するように、プログラム電流I3はアノード端子から駆動用トランジスタ11a1を介して、ソース信号線18bに流れる。プログラム電流I3はソースドライバIC14により発生させられる。

As shown in FIG. 263, the program current I3 flows from the anode terminal to the

プログラム電流I3=10.1μAのうち、プログラム電流I1=10μAは駆動用トランジスタ11a2により供給される。したがって、駆動用トランジスタ11a1はプログラム電流I1とI3の差であるI2=0.1μAの電流を供給する。プログラム電流I2はアノード端子から駆動用トランジスタ11a1を介して、ソース信号線18bに流れる。

Of the program current I3 = 10.1 μA, the program current I1 = 10 μA is supplied by the driving transistor 11a2. Therefore, the driving transistor 11a1 supplies a current of I2 = 0.1 μA, which is the difference between the program currents I1 and I3. The program current I2 flows from the anode terminal to the

プログラム電流I2はコンデンサ19aにより保持される(駆動用トランジスタ11a1がプログラム電流I2を流せるように駆動用トランジスタ11a1のゲート端子に電圧が保持される)。したがって、駆動用トランジスタ11a1にEL素子15に流す電流がプログラムされる。EL素子15に流す電流は0.1μAと小さい。しかし、ソース信号線18a、18bに流す電流は10μAと大きい。したがって、ソース信号線18の寄生容量の影響を受けることなく、EL素子15に流す微小電流を電流プログラムすることができる。

The program current I2 is held by the

第3の状態は、EL素子の電流を供給し、EL素子15が発光している状態である。第3の状態では、図265に示すように、トランジスタ11d1がクローズ状態にされ、他のスイッチ用トランジスタ11はオープン状態にされる。図264に図示するように、駆動用トランジスタ11a1のゲート端子に保持された電圧により、駆動用トランジスタ11a1に電流I2が流れ、EL素子15が発光する。スイッチ用トランジスタ11d1をオンオフ制御することにより、図1などと同様にduty制御を実施することができる。

The third state is a state in which the EL element current is supplied and the

本特許の発明の目的は、トランジスタ特性のばらつきが表示に影響を与えない回路構成を提案するものであり、そのために4トランジスタ以上が必要である。これらのトランジスタ特性により、回路定数を決定する場合、4つのトランジスタの特性がそろわなければ、適切な回路定数を求めることが困難である。レーザー照射の長軸方向に対して、チャンネル方向が水平の場合と垂直の場合では、トランジスタ特性の閾値と移動度が異なって形成される。なお、どちらの場合もばらつきの程度は同じである。水平方向と、垂直方向では移動度、閾値のあたいの平均値が異なる。したがって、画素を構成するすべてのトランジスタのチャンネル方向は同一であるほうが望ましい。 The object of the invention of this patent is to propose a circuit configuration in which variations in transistor characteristics do not affect display, and for that purpose four or more transistors are required. When circuit constants are determined based on these transistor characteristics, it is difficult to obtain appropriate circuit constants if the characteristics of the four transistors do not match. When the channel direction is horizontal and vertical with respect to the major axis direction of laser irradiation, the threshold value and mobility of transistor characteristics are different. In both cases, the degree of variation is the same. The average value of mobility and threshold value differs between the horizontal direction and the vertical direction. Therefore, it is desirable that the channel directions of all the transistors constituting the pixel are the same.

また、蓄積容量19の容量値をCs、第2のトランジスタ11bのオフ電流値をIoffとした場合、次式を満足させることが好ましい。

Further, when the capacitance value of the

3 < Cs/Ioff < 24

さらに好ましくは、次式を満足させることが好ましい。

3 <Cs / Ioff <24

More preferably, it is preferable to satisfy the following formula.

6 < Cs/Ioff < 18

トランジスタ11bのオフ電流を5pA以下とすることにより、ELを流れる電流値の変化を2%以下に抑えることが可能である。これはリーク電流が増加すると、電圧非書き込み状態においてゲート−ソース間(コンデンサの両端)に貯えられた電荷を1フィールド間保持できないためである。したがって、コンデンサ19の蓄積用容量が大きければオフ電流の許容量も大きくなる。前記式を満たすことによって隣接画素間の電流値の変動を2%以下に抑えることができる。

6 <Cs / Ioff <18

By setting the off-state current of the

また、アクティブマトリックスを構成するトランジスタがp−チャンネルポリシリコン薄膜トランジスタに構成され、トランジスタ11bがデュアルゲート以上であるマルチゲート構造とすることが好ましい。トランジスタ11bは、トランジスタ11aのソース−ドレイン間のスイッチとして作用するため、できるだけON/OFF比の高い特性が要求される。トランジスタ11bのゲートの構造をデュアルゲート構造以上のマルチゲート構造とすることによりON/OFF比の高い特性を実現できる。

In addition, it is preferable to adopt a multi-gate structure in which the transistors constituting the active matrix are configured as p-channel polysilicon thin film transistors and the

画素16のトランジスタ11を構成する半導体膜は、低温ポリシリコン技術において、レーザーアニールにより形成するのが一般的である。このレーザーアニールの条件のバラツキがトランジスタ11特性のバラツキとなる。しかし、1画素16内のトランジスタ11の特性が一致していれば、図1などの電流プログラムを行う方式では、所定の電流がEL素子15に流れるように駆動することができる。この点は、電圧プログラムにない利点である。レーザーとしてはエキシマレーザーを用いることが好ましい。

The semiconductor film constituting the

なお、本発明において、半導体膜の形成は、レーザーアニール方法に限定するものではなく、熱アニール方法、固相(CGS)成長による方法でもよい。その他、低温ポリシリコン技術に限定するものではなく、高温ポリシリコン技術を用いても良いことはいうまでもない。また、アモルファスシリコン技術を用いて形成した半導体膜であってもよい。 In the present invention, the formation of the semiconductor film is not limited to the laser annealing method, but may be a thermal annealing method or a method by solid phase (CGS) growth. In addition, the present invention is not limited to the low temperature polysilicon technology, and it goes without saying that the high temperature polysilicon technology may be used. Further, it may be a semiconductor film formed using amorphous silicon technology.

この課題に対して、本発明では図7に示すように、アニールの時のレーザー照射スポット(レーザー照射範囲)72をソース信号線18に平行に照射する。また、1画素列に一致するようにレーザー照射スポット72を移動させる。もちろん、1画素列に限定するものではなく、たとえば、図55のRGBを1画素16という単位でレーザーを照射してもよい(この場合は、3画素列ということになる)。また、複数の画素に同時に照射してもよい。また、レーザーの照射範囲の移動がオーバーラップしてもよいことは言うまでもない(通常、移動するレーザー光の照射範囲はオーバーラップするのが普通である)。

To deal with this problem, in the present invention, as shown in FIG. 7, a laser irradiation spot (laser irradiation range) 72 at the time of annealing is irradiated in parallel to the

画素はRGBの3画素で正方形の形状となるように作製されている。したがって、R、G、Bの各画素は縦長の画素形状となる。したがって、レーザー照射スポット72を縦長にしてアニールすることにより、1画素内ではトランジスタ11の特性バラツキが発生しないようにすることができる。また、1つのソース信号線18に接続されたトランジスタ11の特性(モビリティ、Vt、S値など)を均一にすることができる(つまり、隣接したソース信号線18のトランジスタ11とは特性が異なる場合があるが、1つのソース信号線に接続されたトランジスタ11の特性はほぼ等しくすることができる)。

The pixels are made of three pixels of RGB and have a square shape. Accordingly, each of the R, G, and B pixels has a vertically long pixel shape. Therefore, by annealing the

図7の構成では、レーザー照射スポット72の長さの範囲内に3つのパネルが縦に配置されるように形成されている。レーザー照射スポット72を照射するアニール装置はガラス基板74の位置決めマーカー73a、73bを認識(パターン認識による自動位置決め)してレーザー照射スポット72を移動させる。位置決めマーカー73の認識はパターン認識装置で行う。アニール装置(図示せず)は位置決めマーカー73を認識し、画素列の位置をわりだす(レーザー照射範囲72がソース信号線18と平行になるようにする)。画素列位置に重なるようにレーザー照射スポット72を照射してアニールを順次行う。

In the configuration of FIG. 7, three panels are formed vertically within the range of the length of the

図7で説明したレーザーアニール方法(ソース信号線18に平行にライン状のレーザースポットを照射する方式)は、有機EL表示パネルの電流プログラム方式の時に特に採用することが好ましい。なぜならば、ソース信号線に平行方向にトランジスタ11の特性が一致しているためである(縦方向に隣接した画素トランジスタの特性が近似している)。そのため、電流駆動時にソース信号線の電圧レベルの変化が少なく、電流書き込み不足が発生しにくい。

The laser annealing method described in FIG. 7 (method of irradiating a line-shaped laser spot in parallel with the source signal line 18) is preferably employed particularly in the current programming method of the organic EL display panel. This is because the characteristics of the

たとえば、白ラスター表示であれば、隣接した各画素のトランジスタ11aに流す電流はほぼ同一のため、ソースドライバIC14から出力する電流振幅の変化が少ない。もし、図1のトランジスタ11aの特性が同一であり、各画素に電流プログラムする電流値が画素列で等しいのであれば、電流プログラム時のソース信号線18の電位は一定である。したがって、ソース信号線18の電位変動は発生しない。1つのソース信号線18に接続されたトランジスタ11aの特性がほぼ同一であれば、ソース信号線18の電位変動は小さいことになる。このことは、図38などの他の電流プログラム方式の画素構成でも同一である(つまり、図7の製造方法を適用することが好ましい)。

For example, in the case of white raster display, the current flowing through the

また、図27、図30などで説明する複数の画素行を同時書き込みする方式で均一が画像表示(主としてトランジスタ特性のばらつきに起因する表示ムラが発生しにくいからである)を実現できる。図27などは複数画素行同時に選択するから、隣接した画素行のトランジスタが均一であれば、縦方向のトランジスタ特性ムラはドライバ回路14で吸収できる。 In addition, uniform image display (since display unevenness due to variations in transistor characteristics is unlikely to occur) can be realized by a method of simultaneously writing a plurality of pixel rows described with reference to FIGS. In FIG. 27 and the like, a plurality of pixel rows are selected at the same time. Therefore, if the transistors in adjacent pixel rows are uniform, the transistor circuit unevenness in the vertical direction can be absorbed by the driver circuit.

なお、図7では、ソースドライバ回路14は、ICチップを積載するように図示しているが、これに限定するものではなく、ソースドライバ回路14を画素16と同一プロセスで形成してもよいことは言うまでもない。

In FIG. 7, the

アレイ71の駆動用トランジスタ11aの特性分布は、ドーピング工程でも発生する。図346(a)に図示するように、ドーピングヘッド3461には、ドーピングのための穴が等間隔にあいている。したがって、図346(a)に図示するように、ドーピングによる特性分布が筋状に発生する。本発明の製造方法では、図346に図示するように、ドーピングによる特性の分布方向(図346(a))と、レーザーアニール方向による特性分布方向(図346(b))とソース信号線18の形成方向(図346(c))とを一致させている。以上のように構成(形成)することにより、電流駆動方式において駆動用トランジスタ11aの特性補償を良好に実現できる。

The characteristic distribution of the driving

本発明では特に、駆動用トランジスタ11bの閾電圧Vth2が画素内で対応する駆動用トランジスタ11aの閾電圧Vth1より低くならない様に設定している。例えば、トランジスタ11bのゲート長L2をトランジスタ11aのゲート長L1よりも長くして、これらの薄膜トランジスタのプロセスパラメータが変動しても、Vth2がVth1よりも低くならない様にする。これにより、微少な電流リークを抑制することが可能である。

In the present invention, in particular, the threshold voltage Vth2 of the driving

なお、以上の事項は、図38に図示するカレントミラーの画素構成にも適用できる。図38では、信号電流が流れる駆動用トランジスタ11a、EL素子15等からなる発光素子に流れる駆動電流を制御する駆動用トランジスタ11bの他、ゲート信号線17a1の制御によって画素回路とデータ線dataとを接続もしくは遮断する取込用トランジスタ11c、ゲート信号線17a2の制御によって書き込み期間中にトランジスタ11aのゲート・ドレインを短絡するスイッチ用トランジスタ11d、トランジスタ11aのゲート−ソース間電圧を書き込み終了後も保持するための容量C19および発光素子としてのEL素子15などから構成される。

The above items can also be applied to the pixel configuration of the current mirror shown in FIG. In FIG. 38, the pixel circuit and the data line data are controlled by controlling the gate signal line 17a1 in addition to the driving

図38でトランジスタ11c、11dはNチャンネルトランジスタ、その他のトランジスタはPチャンネルトランジスタで構成しているが、これは一例であって、必ずしもこの通りである必要はない。容量Csは、その一方の端子をトランジスタ11aのゲートに接続され、他方の端子はVdd(電源電位)に接続されているが、Vddに限らず任意の一定電位でも良い。EL素子15のカソード(陰極)は接地電位に接続されている。

In FIG. 38, the

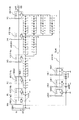

次に、本発明のEL表示パネルあるいはEL表示装置について説明をする。図6はEL表示装置の回路を中心とした説明図である。画素16がマトリックス状に配置または形成されている。各画素16には各画素の電流プログラムを行う電流を出力するソースドライバ回路14が接続されている。ソースドライバ回路14の出力段は映像信号のビット数に対応したカレントミラー回路が形成されている(後に説明する)。たとえば、64階調であれば、63個のカレントミラー回路が各ソース信号線に形成され、これらのカレントミラー回路の個数を選択することにより所望の電流をソース信号線18に印加できるように構成されている(図48を参照のこと)。

Next, the EL display panel or EL display device of the present invention will be described. FIG. 6 is an explanatory diagram focusing on the circuit of the EL display device.

なお、1つのカレントミラー回路の最小出力電流は10nA以上50nAにしている。特にカレントミラー回路の最小出力電流は15nA以上35nAにすることがよい。ドライバIC14内のカレントミラー回路を構成するトランジスタの精度を確保するためである。

The minimum output current of one current mirror circuit is 10 nA or more and 50 nA. In particular, the minimum output current of the current mirror circuit is preferably 15 nA or more and 35 nA. This is to ensure the accuracy of the transistors constituting the current mirror circuit in the

また、ソース信号線18の電荷を強制的に放出または充電するプリチャージあるいはディスチャージ回路を内蔵する。ソース信号線18の電荷を強制的に放出または充電するプリチャージあるいはディスチャージ回路の電圧(電流)出力値は、R、G、Bで独立に設定できるように構成することが好ましい。EL素子15の閾値がRGBで異なるからである(プリチャージ回路については図65、図67およびその説明を参照のこと)。

A precharge or discharge circuit for forcibly releasing or charging the

有機EL素子は大きな温度依存性特性(温特)があることが知られている。この温特による発光輝度変化を調整するため、カレントミラー回路に出力電流を変化させるサーミスタあるいはポジスタなどの非直線素子を付加し、温特による変化を前記サーミスタなどで調整することによりアナログ的に基準電流を調整する(変化させる)。 It is known that an organic EL element has a large temperature dependency characteristic (temperature characteristic). In order to adjust the light emission luminance change due to the temperature characteristics, a non-linear element such as a thermistor or a posistor that changes the output current is added to the current mirror circuit, and the temperature characteristics change is adjusted by the thermistor as an analog reference. Adjust (change) the current.

本発明において、ソースドライバ14は半導体シリコンチップで形成し、ガラスオンチップ(COG)技術で基板71のソース信号線18の端子と接続されている。ソースドライバ14の実装は、COG技術に限定するものではなく、チップオンフィルム(COF)技術に前述のソースドライバIC14などを積載し、表示パネルの信号線と接続した構成としてもよい。また、ドライブICは電源IC82を別途作製し、3チップ構成としてもよい。

In the present invention, the

一方、ゲートドライバ回路12は低温ポリシリコン技術で形成している。つまり、画素のトランジスタと同一のプロセスで形成している。これは、ソースドライバ回路14に比較して内部の構造が容易で、動作周波数も低いためである。したがって、低温ポリシリ技術で形成しても容易に形成することができ、また、狭額縁化を実現できる。もちろん、ゲートドライバ12をシリコンチップで形成し、COG技術などを用いて基板71上に実装してもよいことは言うまでもない。また、画素トランジスタなどのスイッチング素子、ゲートドライバなどは高温ポリシリコン技術で形成してもよく、有機材料で形成(有機トランジスタ)してもよい。

On the other hand, the

ゲートドライバ12はゲート信号線17a用のシフトレジスタ回路61aと、ゲート信号線17b用のシフトレジスタ回路61bとを内蔵する。各シフトレジスタ回路61は正相と負相のクロック信号(CLKxP、CLKxN)、スタートパルス(STx)で制御される(図6を参照のこと)。その他、ゲート信号線の出力、非出力を制御するイネーブル(ENABL)信号、シフト方向を上下逆転するアップダウン(UPDWM)信号を付加することが好ましい。他に、スタートパルスがシフトレジスタにシフトされ、そして出力されていることを確認する出力端子などを設けることが好ましい。なお、シフトレジスタのシフトタイミングはコントロールIC81からの制御信号で制御される。また、外部データのレベルシフトを行うレベルシフト回路を内蔵する。

The

シフトレジスタ回路61のバッファ容量は小さいため、直接にはゲート信号線17を駆動することができない。そのため、シフトレジスタ回路61の出力とゲート信号線17を駆動する出力ゲート63間には少なくとも2つ以上のインバータ回路62が形成されている。

Since the buffer capacity of the

ソースドライバ14を低温ポリシリなどのポリシリ技術で基板71上に直接形成する場合も同様であり、ソース信号線18を駆動するトランスファーゲートなどのアナログスイッチのゲートとソースドライバ回路14のシフトレジスタ間には複数のインバータ回路が形成される。以下の事項(シフトレジスタの出力と、信号線を駆動する出力段(出力ゲートあるいはトランスファーゲートなどの出力段間に配置されるインバータ回路に関する事項)は、ソースドライブおよびゲートドライブ回路に共通の事項である。

The same applies to the case where the

たとえば、図6ではソースドライバ14の出力が直接ソース信号線18に接続されているように図示したが、実際には、ソースドライバのシフトレジスタの出力は多段のインバータ回路が接続されて、インバータの出力がトランスファーゲートなどのアナログスイッチのゲートに接続されている。

For example, FIG. 6 shows that the output of the

インバータ回路62はPチャンネルのMOSトランジスタとNチャンネルのMOSトランジスタから構成される。先にも説明したようにゲートドライバ回路12のシフトレジスタ回路61の出力端にはインバータ回路62が多段に接続されており、その最終出力が出力ゲート回路63に接続されている。なお、インバータ回路62はPチャンネルのみで構成してもよい。ただし、この場合は、インバータではなく単なるゲート回路として構成してもよい。

The

図8は本発明の表示装置の信号、電圧の供給の構成図あるいは表示装置の構成図である。コントロールIC81からソースドライバ回路14aに供給する信号(電源配線、データ配線など)はフレキシブル基板84を介して供給する。

FIG. 8 is a configuration diagram of signal and voltage supply of the display device of the present invention or a configuration diagram of the display device. Signals (power supply wiring, data wiring, etc.) supplied from the

図8ではゲートドライバ12の制御信号はコントロールICで発生させ、ソースドライバ14で、レベルシフトを行った後、ゲートドライバ12に印加している。ソースドライバ14の駆動電圧は4〜8(V)であるから、コントロールIC81から出力された3.3(V)振幅の制御信号を、ゲートドライバ12が受け取れる5(V)振幅に変換することができる。

In FIG. 8, the control signal for the

なお、図8などにおいて14をソースドライバと記載したが、単なるドライバだけでなく、電源回路、バッファ回路(シフトレジスタなどの回路を含む)、データ変換回路、ラッチ回路、コマンドデコーダ、シフト回路、アドレス変換回路、画像メモリなどを内蔵させてもよい。なお、図8などで説明する構成にあっても、図9などで説明する3辺フリー構成あるいは構成、駆動方式などを適用できることはいうまでもない。 8 is described as a source driver in FIG. 8 and the like, but not only a driver, but also a power supply circuit, a buffer circuit (including a circuit such as a shift register), a data conversion circuit, a latch circuit, a command decoder, a shift circuit, an address A conversion circuit, an image memory, or the like may be incorporated. Needless to say, the three-side free configuration or configuration described in FIG. 9 or the like, the driving method, or the like can be applied to the configuration described in FIG. 8 or the like.

コントロールIC81、電源IC82を積載した基板83は、図361に図示するように、封止基板85(封止フタ85)に形成した凹部に、部品などが挿入されるように配置する。図361のように構成することにより、パネルモジュールをコンパクトにできる。

As shown in FIG. 361, the

表示パネルを携帯電話などの情報表示装置に使用する場合、図9に示すように、ソースドライバIC(回路)14、ゲートドライバIC(回路)12は、表示パネルの一辺に実装(形成)することが好ましい(なお、このように一辺にドライバIC(回路)を実装(形成)する形態を3辺フリー構成(構造)と呼ぶ。従来は、表示領域のX辺にゲートドライバIC12が実装され、Y辺にソースドライバIC14が実装されていた)。画面50の中心線が表示装置の中心になるように設計し易く、また、ドライバICの実装も容易となるからである。なお、ゲートドライバ回路を高温ポリシリコンあるいは低温ポリシリコン技術などで3辺フリーの構成で作製してもよい(つまり、図9のソースドライバ回路14とゲートドライバ回路12のうち、少なくとも一方をポリシリコン技術で基板71に直接形成する)。

When the display panel is used for an information display device such as a mobile phone, as shown in FIG. 9, the source driver IC (circuit) 14 and the gate driver IC (circuit) 12 are mounted (formed) on one side of the display panel. (A configuration in which the driver IC (circuit) is mounted (formed) on one side in this way is called a three-side free configuration (structure). Conventionally, the

なお、3辺フリー構成とは、基板71に直接ICを積載あるいは形成した構成だけでなく、ソースドライバIC(回路)14、ゲートドライバIC(回路)12などを取り付けたフィルム(TCP、TAB技術など)を基板71の一辺(もしくはほぼ一辺)にはりつけた構成も含む。つまり、2辺にICが実装あるいは取り付けられていない構成、配置あるいはそれに類似するすべてを意味する。

The three-side free configuration is not only a configuration in which an IC is directly stacked or formed on the

図9のようにゲートドライバ回路12をソースドライバ回路14の横に配置すると、ゲート信号線17は辺Cにそって形成する必要がある。

When the

なお、図9などにおいて太い実線で図示した箇所はゲート信号線17が並列して形成した箇所を示している。したがって、bの部分(画面下部)は走査信号線の本数分のゲート信号線17が並列して形成され、aの部分(画面上部)はゲート信号線17が1本形成されている。

In FIG. 9 and the like, a portion indicated by a thick solid line indicates a portion where the

C辺に形成するゲート信号線17のピッチは5μm以上12μm以下にする。5μm未満では隣接ゲート信号線に寄生容量の影響によりノイズが乗ってしまう。実験によれば7μ以下で寄生容量の影響が顕著に発生する。さらに5μm未満では表示画面にビート状などの画像ノイズが激しく発生する。特にノイズの発生は画面の左右で異なり、このビート状などの画像ノイズを低減することは困難である。また、低減12μmを越えると表示パネルの額縁幅Dが大きくなりすぎ実用的でない。

The pitch of the

前述の画像ノイズを低減するためには、ゲート信号線17を形成した部分の下層あるいは上層に、グラントパターン(一定電圧に電圧固定あるいは全体として安定した電位に設定されている導電パターン)を配置することにより低減できる。また、別途設けたシールド板(シールド箔(一定電圧に電圧固定あるいは全体として安定した電位に設定されている導電パターン))をゲート信号線17上に配置すればよい。

In order to reduce the image noise described above, a grant pattern (a conductive pattern whose voltage is fixed to a constant voltage or set to a stable potential as a whole) is disposed in the lower layer or upper layer of the portion where the

図9のC辺のゲート信号線17はITO電極で形成してもよいが、低抵抗化するため、ITOと金属薄膜とを積層して形成することが好ましい。また、金属膜で形成することが好ましい。ITOと積層する場合は、ITO上にチタン膜を形成し、その上にアルミニウムあるいはアルミニウムとモリブデンの合金薄膜を形成する。もしくはITO上にクロム膜を形成する。金属膜の場合は、アルミニウム薄膜、クロム薄膜で形成する。以上の事項は本発明の他の実施例でも同様である。

Although the

なお、図9などにおいて、ゲート信号線17などは表示領域の片側に配置するとしたがこれに限定するものではなく、両方に配置してもよい。たとえば、ゲート信号線17aを表示領域50の右側に配置(形成)し、ゲート信号線17bを表示領域50の左側に配置(形成)してもよい。以上の事項は他の実施例でも同様である。

In FIG. 9 and the like, the

また、ソースドライバIC14とゲートドライバIC12とを1チップ化してもよい。1チップ化すれば、表示パネルへのICチップの実装が1個で済む。したがって、実装コストも低減できる。また、1チップドライバIC内で使用する各種電圧も同時に発生することができる。

Further, the

なお、ソースドライバIC14、ゲートドライバIC12はシリコンなどの半導体ウエハで作製し、表示パネルに実装するとしたがこれに限定するものではなく、低温ポリシリコン技術、高温ポリシリコン技術により表示パネル82に直接形成してもよいことは言うまでもない。

The

なお、画素は、R、G、Bの3原色としたがこれに限定するものではなく、シアン、イエロー、マゼンダの3色でもよい。また、Bとイエローの2色でもよい。もちろん、単色でもよい。また、R、G、B、シアン、イエロー、マゼンダの6色でもよい。R、G、B、シアン、マゼンダの5色でもよい。これらはナチュラルカラーとして色再現範囲が拡大し良好な表示を実現できる。以上のように本発明のEL表示装置は、RGBの3原色でカラー表示を行うものに限定されるものではない。 The pixels are R, G, and B primary colors. However, the present invention is not limited to this, and may be cyan, yellow, and magenta. Also, two colors of B and yellow may be used. Of course, it may be a single color. Also, six colors of R, G, B, cyan, yellow, and magenta may be used. Five colors of R, G, B, cyan, and magenta may be used. These are natural colors, and the color reproduction range is expanded to achieve a good display. As described above, the EL display device of the present invention is not limited to one that performs color display with the three primary colors RGB.

有機EL表示パネルのカラー化には主に三つの方式があり、色変換方式はこのうちの一つである。発光層として青色のみの単層を形成すればよく、フルカラー化に必要な残りの緑色と赤色は、青色光から色変換によって作り出す。したがって、RGBの各層を塗り分ける必要がない、RGBの各色の有機EL材料をそろえる必要がないという利点がある。色変換方式は、塗り分け方式のようは歩留まり低下がない。本発明のEL表示パネルなどはこのいずれの方式でも適用される。 There are mainly three methods for colorizing an organic EL display panel, and one of them is a color conversion method. It is only necessary to form a blue-only single layer as the light emitting layer, and the remaining green and red colors necessary for full color are generated from blue light by color conversion. Therefore, there is an advantage that it is not necessary to separately coat each layer of RGB, and it is not necessary to prepare organic EL materials of each color of RGB. The color conversion method does not cause a decrease in yield unlike the color separation method. The EL display panel of the present invention can be applied to any of these methods.

また、3原色の他に、白色発光の画素を形成してもよい。白色発光の画素はR、G、B発光の構造を積層することのより作製(形成または構成)することにより実現できる。1組の画素は、RGBの3原色と、白色発光の画素16Wからなる。白色発光の画素を形成することにより、白色のピーク輝度が表現しやすくなる。したがって、輝き感のある画像表示実現できる。

In addition to the three primary colors, white light emitting pixels may be formed. A white light emitting pixel can be realized by forming (forming or configuring) by stacking R, G, and B light emitting structures. One set of pixels includes three primary colors of RGB and a

RGBなどの3原色を1組の画素をする場合であっても、各色の画素電極の面積は異ならせることが好ましい。もちろん、各色の発光効率がバランスよく、色純度もバランスがよければ、同一面積でもかまわない。しかし、1つまたは複数の色のバランスが悪ければ、画素電極(発光面積)を調整することが好ましい。各色の電極面積は電流密度を基準に決定すればよい。つまり、色温度が7000K(ケルビン)以上12000K以下の範囲で、ホワイトバランスを調整した時、各色の電流密度の差が±30%以内となるようにする。さらに好ましくは±15%以内となるようにする。たとえば、電流密度が100A/平方メーターをすれば、3原色がいずれも70A/平方メーター以上130A/平方メーター以下となるようにする。さらに好ましくは、3原色がいずれも85A/平方メーター以上115A/平方メーター以下となるようにする。 Even in the case of forming a set of pixels for three primary colors such as RGB, it is preferable that the areas of the pixel electrodes of the respective colors are different. Of course, if the luminous efficiency of each color is well balanced and the color purity is well balanced, the same area may be used. However, if the balance of one or more colors is bad, it is preferable to adjust the pixel electrode (light emitting area). The electrode area of each color may be determined based on the current density. That is, when the white balance is adjusted within a color temperature range of 7000 K (Kelvin) to 12000 K, the difference in current density of each color is within ± 30%. More preferably, it is within ± 15%. For example, if the current density is 100 A / square meter, the three primary colors are all set to 70 A / square meter or more and 130 A / square meter or less. More preferably, the three primary colors are all set to 85 A / square meter or more and 115 A / square meter or less.

有機EL素子15は自己発光素子である。この発光による光がスイッチング素子としてのトランジスタに入射するとホトコンダクタ現象(ホトコン)が発生する。ホトコンとは、光励起によりトランジスタなどのスイッチング素子のオフ時でのリーク(オフリーク)が増える現象を言う。

The

この課題に対処するため、本発明ではゲートドライバ12(場合によってはソースドライバ14)の下層、画素トランジスタ11の下層の遮光膜を形成している。遮光膜はクロムなどの金属薄膜で形成し、その膜厚は50nm以上150nm以下にする。膜厚が薄いと遮光効果が乏しく、厚いと凹凸が発生して上層のトランジスタ11A1のパターニングが困難になる。

In order to cope with this problem, in the present invention, a light shielding film under the gate driver 12 (in some cases, the source driver 14) and under the

ドライバ回路12などは裏面だけでなく、表面からの光の進入も抑制するべきである。ホトコンの影響により誤動作するからである。したがって、本発明では、カソード電極が金属膜の場合は、ドライバ12などの表面にもカソード電極を形成し、この電極を遮光膜として用いている。

The

しかし、ドライバ12の上にカソード電極を形成すると、このカソード電極からの電界によるドライバの誤動作あるいはカソード電極とドライバ回路の電気的接触が発生する可能性がある。この課題に対処するため、本発明ではドライバ回路12などの上に少なくとも1層、好ましくは複数層の有機EL膜を画素電極上の有機EL膜形成と同時に形成する。

However, when a cathode electrode is formed on the

画素の1つ以上のトランジスタ11の端子間あるいはトランジスタ11と信号線とが短絡すると、EL素子15が常時、点灯する輝点となる場合がある。この輝点は視覚的にめだつので黒点化(非点灯)する必要がある。輝点に対しては、該当画素16を検出し、コンデンサ19にレーザー光を照射してコンデンサの端子間を短絡させる。したがって、コンデンサ19には電荷を保持できなくなるので、トランジスタ11aは電流を流さなくすることができる。レーザー光を照射する位置にあたるカソード膜を除去しておくことが望ましい。レーザー照射により、コンデンサ19の端子電極とカソード膜とがショートすることを防止するためである。

When the terminals of one or

画素16のトランジスタ11の欠陥は、ドライバIC14などにも影響を与える。例えば、図45では駆動用トランジスタ11aにソース−ドレイン(SD)ショート452が発生していると、パネルのVdd電圧がソースドライバIC14に印加される。したがって、ソースドライバIC14の電源電圧は、パネルの電源電圧Vddと同一かもしくは高くしておくことが好ましい。なお、ソースドライバICで使用する基準電流は電子ボリウム451で調整できるように構成しておくことが好ましい。

The defect of the

トランジスタ11aにSDショート452が発生していると、EL素子15に過大な電流が流れる。つまり、EL素子15が常時点灯状態(輝点)となる。輝点は欠陥として目立ちやすい。たとえば、図45において、トランジスタ11aのソース−ドレイン(SD)ショートが発生していると、トランジスタ11aのゲート(G)端子電位の大小に関わらず、Vdd電圧からEL素子15に電流が常時流れる(トランジスタ11dがオンの時)。したがって、輝点となる。

When the SD short 452 is generated in the